# RAFAEL: AN INTELLIGENT, MULTI-TARGET SIGNAL-FLOW COMPILER

by

Gábor Paller

July 31, 1995 Third final version

Technical University of Budapest Department of Electromagnetic Theory, DSP group

## Acknowledgements

First I owe my thesis responsable, Ernő Simonyi thanks for showing me the direction of this thesis and sharing his experience with me during my work. I am especially grateful Klára Cséfalvay for her incredible work in creating the DSP group at the Department of Electromagnetic Theory and helping me when I was lost. I say a big THANK YOU to all the members of the DSP group whose enthusiasm brought and brings forward the projects of this group.

From the French part my thanks go first to Christophe Wolinski who was professionally responsible for my final 9 month stay at IRISA, Rennes. Valuable comments, critiques, helps of Christophe greatly contributed that this thesis is at least readable ... I am very grateful to Paul Le Guernic, head of the EP-ATR project in IRISA for accepting me in his group during my stay in IRISA and for carefully following my work. I must hereby thank all members of the EP-ATR group who showed me hope when I got lost in the details of the SIGNAL language and its compiler. I am obliged the Government of France which provided the scholarship for the stay at IRISA.

I am also obliged Christophe Lavarenne and Yves Sorel from the SynDEx team of INRIA, Rocquencourt who provided a one month stay at INRIA and helped me to develop the routing aspects of the Springplay scheduler.

At last I recall all the friends, acquintances and hitchhikers who made the stay on the Land of Bretons unforgettable.

| Gábor Paller |  |  |

|--------------|--|--|

|              |  |  |

# Contents

| 1 | Intr | oducti | ion                                                  | 3  |

|---|------|--------|------------------------------------------------------|----|

|   | 1.1  | The ai | im of the Rafael project                             | 3  |

|   | 1.2  | The d  | ataflow approach                                     | 6  |

|   |      | 1.2.1  | Dataflow paradigm                                    | 6  |

|   |      | 1.2.2  | Synchronous, boolean and integer-controlled dataflow | 8  |

|   |      | 1.2.3  | From dataflow graphs to directed acyclic precedence  |    |

|   |      |        | graphs                                               | 10 |

|   |      | 1.2.4  | Partitioning and scheduling                          | 12 |

|   | 1.3  | Synch  | ronous dataflow languages                            | 13 |

|   |      | 1.3.1  | ESTEREL                                              | 14 |

|   |      | 1.3.2  | LUSTRE                                               | 17 |

|   |      | 1.3.3  | SIGNAL                                               | 20 |

|   |      | 1.3.4  | ${ m SFG}$ generation from synchronous description   | 25 |

| 2 | The  | static | scheduling problem                                   | 27 |

|   | 2.1  | Proble | em formalization                                     | 27 |

|   | 2.2  | Static | scheduling methods                                   | 31 |

|   |      | 2.2.1  | ASAP and ALAP schedules                              | 31 |

|   |      | 2.2.2  | Integer Linear Programming (ILP)                     | 32 |

|   |      | 2.2.3  | Branch & Bound algorithms                            | 34 |

|   |      | 2.2.4  | General List Schedulers                              | 36 |

|   |      | 2.2.5  | Graph partitioning algorithms                        | 38 |

|   | 2.3  | The R  | tafael heterogeneous list scheduler (RHLS)           | 40 |

|   | 2.4  |        | pelined Springplay algorithm                         | 42 |

|   |      | 2.4.1  | Principles of the Springplay algorithm               | 44 |

|   |      | 2.4.2  | Execution time minimizing component                  | 48 |

|   |      | 2.4.3  | Communication cost component                         | 49 |

|   |      | 2.4.4  | Parallelism optimization                             | 50 |

|   |      | 2.4.5   | Anchoring nodes                           |

|---|------|---------|-------------------------------------------|

|   |      | 2.4.6   | Fixpoint generation                       |

|   |      | 2.4.7   | Complexity                                |

|   |      | 2.4.8   | Performance evaluation                    |

|   | 2.5  | Spring  | play with enhanced communication model 56 |

|   | 2.6  |         | ed Springplay algorithm                   |

|   |      | 2.6.1   | Changes in the algorithm principles 69    |

|   |      | 2.6.2   | Processor balance component               |

|   |      | 2.6.3   | Explicit delay elimination component      |

|   |      | 2.6.4   | Results of PLSP's testing                 |

|   | 2.7  | Conclu  | sion on the Springplay algorithms         |

| 3 | Rafa | ael SF  | G compiler 81                             |

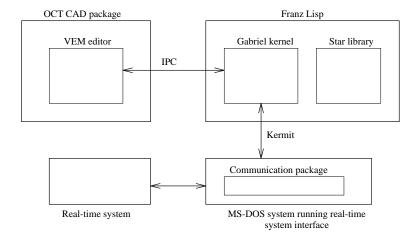

|   | 3.1  | Existin | ng SFG compilers                          |

|   |      | 3.1.1   | Gabriel                                   |

|   |      | 3.1.2   | Ptolemy                                   |

|   |      | 3.1.3   | SynDEx                                    |

|   | 3.2  | Rafael  | basic structure                           |

|   |      | 3.2.1   | Major design considerations 90            |

|   |      | 3.2.2   | The structure of the Rafael system 91     |

|   |      | 3.2.3   | Rafael nodes and connections              |

|   |      | 3.2.4   | Rafael software model                     |

|   |      | 3.2.5   | Rafael hardware model                     |

|   | 3.3  | The in  | ternal structure of the Rafael system 100 |

|   |      | 3.3.1   | Graph description language                |

|   |      | 3.3.2   | The database                              |

|   |      | 3.3.3   | Rafael memory management 107              |

|   |      | 3.3.4   | Compiler passes                           |

|   |      | 3.3.5   | Code generation model                     |

|   | 3.4  | Conclu  | sions on the Rafael project               |

|   |      |         |                                           |

## Chapter 1

# Introduction

## 1.1 The aim of the Rafael project

Writing programs for the modern Digital Signal Processors (DSPs) introduces difficult tasks for the software engineers because a painful tradeoff exists between the computing power and the productivity/task complexity. Unfortunately the existing and well-known higher level programming environments (for example the "C" language) performs very poorly on the DSP platforms because being general languages they cannot exploit the special capabilities of the DSPs (circular buffers, parallel instructions and so on) or avoiding pipeline effects. This can cause extremely high performance loss (can be as much as 1000% compared to the assembly realization). Several developments were made to improve C compilers on DSP platforms [Lear90] but generally they use system or DSP dependent language extensions and their performance is still not really convincing. So the developers have to choose - writing the DSP code in assembly for achieving higher performance thus lower hardware cost or using a high-level environment which will speed up the development but decrease the efficiency of the DSP so that more expensive DSP-s must be chosen. It can even happen that the problem cannot be solved on high level.

The other problem is the embarassing abundance of DSP architectures and languages. One often faces the problem of porting existing results onto other DSP platforms. If the code is written in assembly , this will be a long and tiresome process. Some "common language" is needed but not having efficiently realizable high level platform this solution does not seem to be promising. Nowadays the solution is sought toward optimized software

libraries (like the SPOX math libraries) which try to combine the power of assembly routines with the efficiency of C. SPOX [Spox88] does accelerate the developing process but it is a fixed set of routines and if we extend it (for example we need an arithmetic routine or new algorithm that the SPOX cannot offer) we still have to write it in assembly loosing the portability.

Nowadays the parallel DSP is in the focus of attention, first of all because real-world DSP problems often require immense computing power. A number of existing DSPs can be used for parallel realizations, some of them has been designed especially for parallel computing for example Texas Instrument's TMS320C40, TMS320C80 and Analog Devices ADSP21060. The task scheduling is an important part of the multiprocessor implementation of DSP algorithms. This equally means partitioning the tasks among multiple DSPs and scheduling the tasks on each DSP. Generally parallel programs are scheduled "by hand" in the existing parallel development systems which is a difficult task and in the case of more complex tasks it cannot be done effectively. The other approach used frequently in the existing DSP operating systems uses the well proven real-time operating system scheme (sometimes timesliced scheduling is added) [Spox88, Virt93]. This scheme is based on separate tasks and a task scheduler program which changes the tasks when it is necessary. This task scheduler requires processing time.

Speciality of the DSP algorithm is that they don't require much run-time decisions. Very handy description form of these algorithm is the signal-flow graph (SFG). We will give later a more thorough definition, here we only mention that the signal-flow graph is a graphical description of an algorithm in which computations are represented by graph nodes and dependencies among the computations by graph branches. If we can cluster enough nodes together that their dependency graph and execution time do not depend on the input values, we can schedule in compile time thus eliminating the processor load of the dynamic scheduler.

An important, emerging feature of the DSP code generators whether or not they support heterogeneous target systems. This requirement arises because of the need of cost-effective design (using more expensive DSPs only if we need and replacing less-loaded ones by cheaper processors) and the new research area, the hardware-software co-design. Co-design means that the software and hardware partitioning decisions are not fixed at an early stage of development but the software and hardware design proceed in parallel interacting with each other [Kala93]. A design software supporting this technique should provide design model(s) which allow the separation of software and hardware as late as possible. This technique has very important

practical aspects now with the DSP-core libraries when the designer can use an industry-standard DSP-core (for example the TMS320C20) on his or her custom circuit.

As it is shown in the literature, more complex SFGs can be as difficult to overview or debug as a program coded in a traditional way. Formal languages are able to prove certain properties of their input programs so it is a lucrative idea to use them for checking if there are semantic errors in the SFG. The problem can be described in a formal language and the SFG can be generated by the compiler of the formal language.

Thus, the DSP code generation problem is the following: we need a system which is flexible enough to be adapted to several existing DSP platforms, avoids the power loss of the high-level languages, solves the partitioning and scheduling problems and in addition it is easy-to-use for the DSP algorithm developer who is generally not a programmer. A proposition for this problem will be presented in this document describing Rafael, an intelligent code generator based on signal flow graphs.

Rafael was designed as a small, flexible system which can run even on very small computers (it is implemented under Microsoft Windows on IBM PC compatible computers). It is a SFG compiler integrated into a simple framework which allows DSP algorithms to be described in SFG form and the compiler translates this description into program for a heterogeneous multiprocessor hardware. The compiler distributes the SFG on the multiprocessor system, schedules the operations on each processor, creates the communication scheme among the processors and generates executable assembly source program for each processor. Rafael features a programmable DSP database and code generator library so it can be adapted easily to any processor. Small resources of the host computer do not allow us to compete with the comprehensive features of existing SFG compilers hosted on workstations but we hope to prove that Rafael can compete successfully on several domains with those systems.

This document will be structured as follows:

- In the following part of Introduction we present the dataflow approach, we deal shortly with its problems in the case of graphs containing run-time decisions and we present the synchronous dataflow language concept which allows us to generate consistent dataflow graphs with simpler structure.

- In chapter 2 we will deal with the static scheduling problem, we present the schedulers used in Rafael and the Rafael schedulers will be com-

pared to other existing scheduler algorithms. As no existing scheduler could produce acceptable performance on heterogeneous architectures, a new scheduler class called Springplay has been devised. The chapter deals with this algorithm in details.

• In chapter 3 the internal structure of Rafael will be described and it will be compared to other existing SFG compilers.

## 1.2 The dataflow approach

### 1.2.1 Dataflow paradigm

The dataflow concept was proposed for its visuality which matches well to certain problems (Digital Signal Processing, for example) and for its capability to reveal the available parallelism. In dataflow, program is represented as directed graph where vertices represent computations (we will call them operations sometimes they are called actors [Lee87] in the literature) and branches represent FIFO channels that queue data values. These branches show the signal paths where a signal is simply an infinite stream of data and each data token is called a sample. An operation is activated by a given number of tokens on its inputs and it is fired (the computation assigned to the operation is executed) then it produces tokens on its outputs. These tokens may remain in the system for some time in the branch FIFOs before they are consumed by other operation.

The earliest reference to the dataflow paradigm appears to be the computation graphs of Karp and Miller [Karp66]. Each node has an associated function for computing outputs from inputs and each branch has four associated integer values:

- $A_p$ , the number of data words initially in the queue associated with the branch,

- $U_p$ , the number of data words written into the queue when the node connected to the input of the branch is executed,

- $W_p$ , the number of data words removed from the queue when the node connected to the output of the branch is executed,

- $T_p$ , a threshold giving the minimum queue length necessary for the output node to execute. We require  $T_p \geq W_p$ .

Karp and Miller prove that computation graphs with these properties are determinate (the sequence of data values produced by each node does not depend on the order of execution of the actors provided that the order of execution is valid). They also dealt with problems of determining the size of branch queues and the conditions that cause computations to terminate. (Later it became more important to avoid the deadlocks in the dataflow graphs so that computations can continue indefinitely). It is shown that Karp and Miller computation graph model can be analyzed in the terms of Petri nets [Buck93b].

The first papers about the usage of dataflow principles for the developement of computer architectures and programming languages were presented by Dennis [Denn75]. Dennis applied the concepts of dataflow to computer architectures thus creating the dataflow computer architecture. The first machine using this concept was built by Davis [Dav78]. There are two basic types of dataflow computers: static and dynamic or tagged token dataflow computers. The main difference between the two types is that in the static version at most one token is allowed on every branch and the storage of the edges is allocated at compile-time while in the dynamic version there is no such limitation and the storage for the branch queue is allocated dynamically. The biggest problem of the pure dataflow model is the excessive token matching and communication overhead between the operations. Hybrid models have been developed which group the operations into threads if possible and execute them sequentially [Bic91].

A data flow graph can be large or fine grain one [Lee87]. Fine grain data flow means that the operations are atomic computations like adders, multipliers while large grain data flow (also called block diagrams) are composed of more complex components like FFTs, filter blocks, etc. The granularity of the graph determines the amount of parallelism that can be exploited. We consider the basic operations undivisible and no effort is made to exploit the parallelism inside an operation.

An operation can be also a graph of operations, in this case the graph is hierarchical. By the most common approach hierarchical graphs are flattened (the hierarchy is destroyed) [Buck94] so that maximal parallelism be present. There are efforts, however, that the design system find the best granularity by itself [Hoan93].

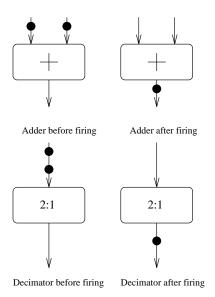

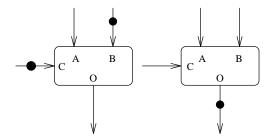

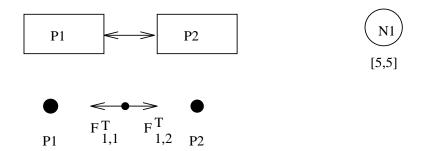

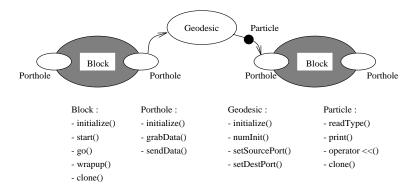

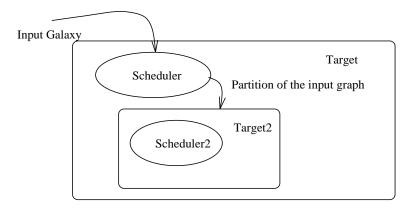

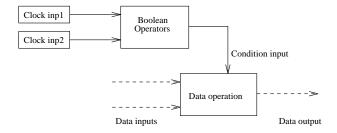

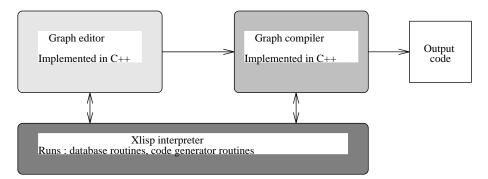

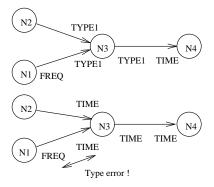

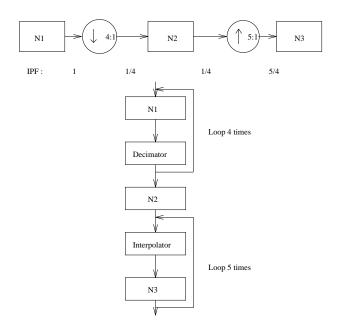

#### 1.2.2 Synchronous, boolean and integer-controlled dataflow

We call operations of the graph synchronous if they consume and produce constant amount of tokens when fired and the number of the tokens is known at compile time. (fig. 1.1) This restriction results in a big advantage that the control flow is completely deterministic, thus the scheduling can be accomplished in compile time. This approach can be used to describe a big number of DSP applications as they require no or little run-time decision making. As it was pointed out in [Buck93a], however, "little" is not the same as "none". Therefore, synchronous data flow (SDF) is not capable of describing important classes of problems. The traditional SDF approach was extended by conditional operations like SWITCH and SELECT (fig. 1.2). A dataflow graph containing these binary-controlled conditional operations is called boolean dataflow graph (BDF).

Figure 1.1: Synchronous Dataflow operations

In [Lee87] the foundations of compiling SDFs into sequential programs have been developed. The following questions can be asked about any dataflow graph:

1. Do cyclic schedules exist? A cyclic schedule is a sequences of actor executions that return the graph to its original state.

SELECT operator before and after firing The value of the token on C input selects whether the tokens on A or B input will be emitted  $\,$

SWITCH operator before and after firing

The value of the token on C input selects whether the next token on I will be emitted on A or B outputs

Figure 1.2: Boolean Dataflow operations

- 2. Does the graph have bounded cyclic schedule? The schedule length bound is important when generating code for a real-time environment.

- 3. Does the graph deadlock? In deadlock situation there is no operation that can be executed.

- 4. Can the graph be scheduled to use bounded memory?

A graph complying with these conditions is called *consistent*.

In [Lee87] algorithms are presented to answer all four questions for any graphs. The problem is more complicated in the BDF case.

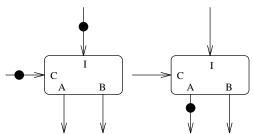

[Buck93b] introduces an enhanced version of BDF, the Integer-controlled dataflow (IDF). BDF is extended by two new operations. The first is the CASE-ENDCASE structure which is similar to the SWITCH-SELECT pair with the distinction that the control branch consumes integer-valued tokens and CASE-ENDCASE have more outputs and inputs. The second is the REPEAT operation which repeatedly emits the input token and the number of repetitions is determined by the integer-valued token on the control branch. As the BDF model is already Turing-equivalent, these new operations do not extend the number of the algorithms that can be modelled but in several cases they simplify greatly the dataflow graph.

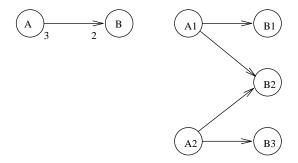

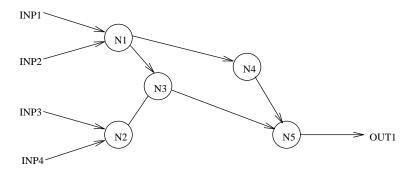

# 1.2.3 From dataflow graphs to directed acyclic precedence graphs

Dataflow graphs are not directly suitable for scheduling. The scheduler algorithm accepts a directed acyclic precedence graph (APEG) in which the firing precedence constraints of the operations has already been determined. As described in the previous section, the dataflow-precedence graph transformation is the central question of the dataflow graph theory.

In figure 1.3 a dataflow graph and the corresponding APEG are depicted. In the SDF case the problem is solved in [Lee87] by means of the balance equations. By solving these equations one can determine the number of operation firings so that the tokens consumed and produced on each branch be equal. It is convenient to express these equations in matrix form. First we define the topology matrix which has one row for each branch and one column for each operation of the graph. A  $\gamma_{i,j}$  element of this matrix  $\Gamma$  determines how many tokens are added by operation i to branch j. It  $\gamma_{i,j}$  is negative if the operation consumes from that branch. This matrix is the following for the graph in figure 1.3.

Figure 1.3: Dataflow graph and the corresponding APEG

$$\Gamma = \begin{bmatrix} 3 & -2 \end{bmatrix}$$

Now we look for the  $repetition\ vector\ \vec{r}$  which solves the following equation:

$$\Gamma \vec{r} = \vec{0} \tag{1.1}$$

We find that all the non-trivial solutions have the form:

$$\vec{r} = k \begin{bmatrix} 2 \\ 3 \end{bmatrix}$$

which means that operation A should be executed twice while operation B three times to bring back the graph to its original state. The graph is inconsistent if equation 1.1 has only trivial solution.

If we have the repetition counts for each operations, the simplest algorithm to construct the APEG corresponding to the dataflow graph is a kind of list scheduler [Buck93b]. We maintain a "schedulable operation list" and we initialize this list at the beginning to the operations with no inputs or having sufficient initial tokens at their inputs for firing. We then add them one by one to the APEG with their data dependencies. Adding an operation to the graph may enable others and they are inserted into the schedulable operation list.

For example in the case of the graph in figure 1.3 operation A can be placed twice at once. After this step instances of operation B are allowed to be placed. As B1 consumes two only tokens of A1 so dependency branch must be added between A1 and B2 as well. B2 cannot be satisfied with the remaining one token of A1 so it will depend on A2 too. Then B3 can be

placed which consumes only from A2. More systematic algorithm can be found in [Lee87].

Whole thesises have been written on the questions of dataflow-APEG transformations in more complex cases [Buck93b, Bhat94a]. In the BDF case two important class of constructs, nested if-then-else and loops were shown to be "well-behaved" in the sense that a BDF using only these macro-constructs has always bounded memory requirement [Gao92]. In [Buck93a, Buck93b] more indulgent conditions are presented for the BDF graph to be consistent based on probabilistic analysis and clustering techniques. Probabilistic analysis is shown to produce unreliable results and the essence of clustering is to find basic constructs in the graph. As "well-behaved" graphs cover the most important algorithm constructs, accepting the restrictions in [Gao92] does not seem to cause many problems. [Buck93b] extended the probabilistic techniques to IDFs as well.

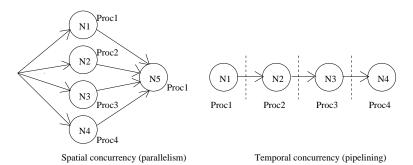

#### 1.2.4 Partitioning and scheduling

If the dataflow graph is static (it contains no runtime decision making) operations can be assigned to processors and arranged on them statically so runtime scheduler is not needed. It is such a big advantage that hybrid solutions were presented that allows partial static scheduling even if there are runtime decisions [Buck91]. The scheduling problem is shown to be NP-complete [Sark89], heuristics are used to provide good-quality solutions in acceptable time.

Two main approaches exist for the partitioning and scheduling task as the problem is slightly different in the VLSI (called data path synthesis) and the programmable DSP case. In the VLSI case we are allocating specialized, low-level resources which can accomplish only one task type (adders, multipliers). In the synchronous case communication takes no time and the restriction that the duration of every operation is one control step is often acceptable. In the programmable DSP case we have much fewer resources that can accomplish many types of tasks (up to very complex operations like FFTs) and the communication must be accounted for. In this thesis we will mainly concentrate on the programmable DSP case (as the Rafael design system supports actually only these kinds of devices) but we will refer all the time to the very similar data path synthesis problems.

Major part of this thesis will be devoted to the static partitioning and scheduling problem. We already have the APEG and we have a description of resources in the target hardware. The goal is to find an assignment of op-

erations in the APEG to resources (partitioning) and an order of operations assigned to a resource (scheduling) which is optimal in some sense. In many cases we will simply use the inexact term scheduling problem which includes both tasks.

The target system can consists only of the same type of processing units, in this case we call our task *homogeneous scheduling problem*. If the execution time of an operations may depend on the processing unit which executes it, we face the much more complicated *heterogeneous scheduling problem*.

The heterogeneous scheduling problem has many practical aspects. First, it is a common practice to use less powerful (thus less expensive) processors and prescribe cheaper DSPs for subtasks which cannot exploit the capabilities of a bigger DSPs. Second, a very important (and fashionable) research area is the development of co-design methods. Co-design means that the output of a design process is a mixed hardware-software realization. An intelligent design software may decide, which part is to be realized in hardware and which in software and it has to generate circuit descriptions/programs. This design method gained considerable importance with the introduction of DSP cores - cell libraries containing entire DSPs that can be embedded into one's circuit design. Co-design results in integration of heterogeneous systems so it involves heterogeneous schedululing. Chapter 2 will deal with the scheduling problem in details presenting solutions to the less-researched heterogeneous case.

## 1.3 Synchronous dataflow languages

There is a big problem with the dataflow approach, the properties of the BDF graphs cannot be proven in every case. As we could see in the previous sections, static dataflow graphs can be proven quite easily but it holds true only for some classes of BDFs. Proving one's input algorithm is very important in the case of complex, time critical programs. This need inspired the creation of synchronous dataflow languages which are based on simple but deep mathematical principles so certain properties of the programs can be proven. The class of the systems to which these languages were developed is the reactive system class. We call systems reactive if they maintain permanent interaction with their environment. In addition, we use the word real-time if there are timing constraints defined.

The basic idea behind the synchronous approach is simple: we suppose ideal reactive systems in which internal processing takes no time. If out-

put signals are emitted at a certain time instant, they will be produced at the same time, synchronously with the input signals. We call a system reactive if it interacts continuously with its environment, it receives input events and produces output events. Note that this approach uses the "synchronous" word differently to the usage of this word by the dataflow terminology. Big advantage of this approach is that ideal synchronous systems can be decomposed into components without affecting the behaviour of the system. The first introduction of synchronous concept for software appeared in [Berr83, LeG86]. One of the best surveys of the topic is [Benv91].

There exists a set of actual machines for which the ideal synchronous model can be applied immediately. Fast processors in slow environments are handy examples for this. For example a VLSI realization with some 10 ns cycle time can give almost instantenous response. [Benv91] shows how the synchronous approach can be used to describe asynchronous systems like dataflow graphs.

There are two families of synchronous languages.

- State based languages like ESTEREL [Bous91]. ESTEREL modelizes state machines by instantaneous broadcast events which bring the machines into new states.

- Multiple Clocked Recurrent Systems (MCRSs) like SIGNAL [LeG91] and LUSTRE [Halb91]. These languages describe the state transition diagram to be modelized by means of recurrent equations. This approach is obvious for discrete time systems.

Synchronous languages provide an efficient tool for generating data flow graphs whose properties are proven.

We will introduce three dataflow languages in short here.

#### 1.3.1 ESTEREL

The basic notion of ESTEREL (similarly to other dataflow languages) is the "signal". Signal is a stream of time instants at which a signal can be present or missing. If a signal is present, it can also have a value. All the synchronous dataflow languages share the common notion that the input signals provoke instantaneous reaction.

The reaction mechanism of ESTEREL is based on *broadcasts*. Broadcast is a signal which can be seen by every receptors in the program. Broadcasts can emit signals that can be tested for presence, value, etc. The emitted

signal is restricted to a given time instant and is received as present by all the receptors during this instant. Example :

```

present T then emit U end

||

emit S

||

present S then emit T end

```

The || delimiter creates parallel tasks. Signal S is broadcasted by the emit statement, it is received by the present S which in turn emits T. Signal T is then emitted and is received by present T which emits U. At the end all the signals S,T and U are emitted at the same instant.

The most basic ESTEREL structure is the  $generalized\ watchdog$ . Its form is the following :

```

do loop\ body watching signal

```

This structure executes the loop body until

- 1. The loop body terminates

- 2. The signal argument to the watching arrives

```

Example:

```

```

do

await INPUT;

emit OUTPUT

watching TERM

```

The await statement waits for the INPUT signal. As soon as this signal arrives, the emit statement emits the OUTPUT signal. The watching structure guarantees that the body be interrupted as the TERM signal is raised. The structure can be extended by the timeout part which is executed if the loop body is terminated by the watched signal. Example:

```

do

await INPUT;

emit OUTPUT

watching TERM

timeout emit TIMEOUT

```

The TIMEOUT signal will be emitted only if TERM arrives before INPUT. Other basic structure is the trap. We may have:

```

trap SIG in

await INPUT;

emit OUTPUT;

exit SIG

end

```

This structure waits for INPUT, emits OUTPUT then it is preempted by the exit SIG statement.

The ESTEREL compiler [Est88] uses effective compilation algorithms [Gonth88] to eliminate the programs with certain semantical problems, for example deadlocks, short circuits. This is done by means of a potential function that administrates which signals can or cannot be emitted at a certain instant. This is used for ordering the signals so that a sequential execution scheme can be generated. If this order cannot be established, casuality problem is signaled. This approach is called execution semantics.

Other, more exact proofing method of ESTEREL is based on the behavioral semantics [Plot81]. This semantic works with transitions which are described in the following general form:

$$\begin{array}{ccc} & Input/Output \\ Program & \longrightarrow & NewProgram \\ & Terminated \end{array}$$

This notation means the following: if the input event is *Input*, *Program* reacts by producing *Output* and goes to the new state so that at the next instant *NewProgram* will be executed. Inference rules are used to construct compound statements. The example rules for do ... watching taken from [Bous91]:

$$I/O \ p \stackrel{I/O}{\longrightarrow} q \ ext{true}$$

do  $p$  watching  $S \stackrel{}{\longrightarrow}$  nothing

The rule above means that if we suppose that the body p terminates, the watching terminates too leaving nothing as residual program.

If the body p does not terminate, S is tested for presence at the next instant and loop body q is executed if S is not present.

The inference rules presented above are used for building *proof trees*. Inference rules are used systematically by the reasoning system for finding out properties of the program.

The ESTEREL compiler translates the program into finite state machines which can be implemented very efficiently. In the resulting program parallelism and local communications are transformed into sequential code. ESTEREL compiler is also able to produce conditioned dataflow graph that in common format with other dataflow languages. We will deal with this format in chapter 2.

Realizing the unability of the synchronous languages when handling asynhronous distributed algorithms in [Berr93] a new extension of ESTEREL is presented in which they integrate the synchronous ESTEREL with CSP [Hoar85]. CSP is an asynchronous language using classical interprocess communications like rendezvous. New CSP-like statements are:

#### channel C;

which declares a communication channel called C and

#### rendezvous L : C;

which accomplishes a rendezvous on channel C. The L parameter is an optional label. Three signals are automatically created by the rendezvous statement:  $\mathbf{sL}$ ,  $\mathbf{L}$  and  $\mathbf{kL}$ ,  $\mathbf{sL}$  is used to request the rendezvous on C,  $\mathbf{L}$  is used for signaling the completion of the rendezvous while  $\mathbf{kL}$  signals abandoning the rendezvous request. A given channel can accomplish only one rendezvous at a time. The referenced paper includes the new operations into the behaviorial semantics.

#### 1.3.2 LUSTRE

As LUSTRE and SIGNAL (which will be described in section 1.3.3) are very similar, we will describe LUSTRE [Halb91] very shortly. As in the case of

every dataflow language, LUSTRE works on signals. Signals in LUSTRE are valued data streams, at a certain instant a signal can be *absent* so that it does not have value or *present* when it holds a value. We can approach it from an other direction: a signal is composed of two data streams: a *clock* which determines the instants of the signal's presence and a *data stream* which carries the values. Data in that stream can be absent. The most important restriction of LUSTRE to SIGNAL is that all the signals have one common clock.

LUSTRE is a definitional language. It means that a

$$0 = I;$$

should be considered in the equational sense, not as a declarative assignment. It is the so called *substitution principle*, O can be substituted with I anywhere in the program and conversely. As a consequence, equations can be written in any order, it will not change the meaning of the program.

Types are usually imported from the "host language", the language to which the LUSTRE compiler translates. Usual operations are avilable on these types. A bit less usual operation is the if ... then ... else structure. An example:

#### if E < 0 then X+1 else 0

which means that **E** and **X** has the same clock and this will be the clock of the result as well. At the *n*th instant the result will have the value of  $X_n + 1$  if  $E_n < 0$  else 0.

The operation set is extended by "temporal" operators.

#### • Delay

pre which realizes a delay. If the data stream of I is  $(i_1, i_2, i_3, ..., i_n, ...)$  then pre(I) will be the sequence  $(nil, i_i, i_2, ..., i_{n-1}, ...)$ . The first nil denotes the value of an uninitialized memory.

#### • Initialization

-> (followed by). Let I and F be two signals with the same clock then I->F will be always equal to F except for the first instant when it is I.

#### • Downsampling

when, downsampling. If I is a signal and F is a boolean signal with the same clock, I when F will have the clock of F but it will have absent value whenever F is false. If F is true, the result will be the value of I in that instant. See figure 1.3.2.

#### Interpolation

current interpolates the signal. current I has the value of I if it is present else it holds the last value of I when it was present. The statement is illustrated in figure 1.3.2.

| F        | true  | true  | false | false | true  |

|----------|-------|-------|-------|-------|-------|

| I        | $x_1$ | $x_2$ | $x_3$ | $x_4$ | $x_5$ |

| I when F | $x_1$ | $x_2$ |       |       | $x_5$ |

Figure 1.4: The operation of when in LUSTRE

| I         | $x_1$ | $x_2$ |       |       | $x_5$ |

|-----------|-------|-------|-------|-------|-------|

| current I | $x_1$ | $x_2$ | $x_2$ | $x_2$ | $x_5$ |

Figure 1.5: The operation of current in LUSTRE

Assertion is a speciality of LUSTRE. One can define some known properties of the environment and it may influence program optimization and verification. We can say for example that a certain signal is never negative.

```

assert (x >= 0);

```

LUSTRE groups equations into *nodes*. A node is a part of the dataflow operations collected into one unit with parameter header and local variables. For example a FIR filter node would look like the following:

```

const a1,a2,a3:real.

node FIR(x: real) returns(y: real)

var r1,r2:real;

let

r1 = (0. -> pre(x));

r2 = (0. -> pre(r1));

y = a1*x + a2*r1 + a3*r2;

tel.

```

LUSTRE compiler uses several program proofing methods, beside the common semantical analysis (number of variable definitions, absence of recursive calls, loop-free definitions) LUSTRE introduces clock calculus. This

calculus is used to prove that operator arguments have the same clock and the clock of any operands of the current operator is not the basic clock of the node. LUSTRE uses a simple scheme for proving clock equality, it substitutes the signal definitions when a derived signal is used in an equation then compares the resulting expressions. For example:

```

y = b+c;

a1 = 0.-> b+c;

a2 = 0.-> y;

```

After the substitution of b+c in the place of y we will have two identical equations.

The actual LUSTRE compiler produces a graph format common to ES-TEREL. From this format code generators can be used to translate toward C, Lisp and ADA.

#### 1.3.3 SIGNAL

SIGNAL language was presented in [LeG86, LeG91]. SIGNAL is based on very similar principles to LUSTRE. The main difference between SIGNAL and LUSTRE is the introduction of missing signal state denoted as  $\bot$ . This allows SIGNAL systems to be multi-clocked in the sense that the clock of signals can be different. Each signal is associated a clock which can be present or  $\bot$  at a certain instant. Each time the clock is present, the signal has value. SIGNAL is based on only 5 kernel constructions.

#### • Instantaneous function calls

```

Y := f(X1, \ldots, Xn)

```

The basic functions defined by the host language are extended to signals. This is a monochronous operator,  $Y, X_1, X_2, ..., X_n$  have the same clock. The function call is instantaneous so an Y value calculated from X values of a time index n will have the same n time index.

#### • Delay

The delay operator is used to create index shift between its input and output signal. This operator is also monochronus, the clock of its output is the same as the clock of its input.

$$Y := X \$ 2$$

will result in

$$\forall n > 1$$

$y_n = x_{n-2}$

The initial value of the delay can be prescribed when declaring the variable.

#### integer Y init 0

The behaviour of the delay operator above is shown in figure 1.3.3 (supposing 0 initial value)

| X | $x_1$ | $x_2$ | $x_3$ | $x_4$ | $x_5$ |

|---|-------|-------|-------|-------|-------|

| Y | 0     | 0     | $x_1$ | $x_2$ | $x_3$ |

Figure 1.6: The operation of delay in SIGNAL

#### • Extraction

Extraction operator is used very similarly to that of LUSTRE to down-sample a certain signal driven by a boolean gate signal. If X is any signal, B is a boolean-valued signal which has true or false values, the output will have the value of X at time instants when both X and B are present and B is true. This operator is called polychronous as it allows operands with different clocks.

#### Y := X when B

Time diagram 1.3.3 illustrates the operation of when.

| X | $x_1$            | 1    | $x_3$ | $x_4$ | $x_5$            |

|---|------------------|------|-------|-------|------------------|

| В | true             | true | false | 1     | true             |

| Y | $\overline{x}_1$ | 1    | 1     | 1     | $\overline{x}_5$ |

Figure 1.7: The operation of when in SIGNAL

#### • Deterministic merge

This operator allows merging its two input signal with priority. If A and B are two signals,

#### Y := A default B;

will produce an Y signal which has the values of A whenever A is present and if A is not present but B is, Y has the value of B. The instant set of the resulting signal is the union of the instant set of the input signals and priority is given to A if both inputs are present. Figure 1.3.3 illustrates the operation of default.

|   | A | $a_1$ | 1     | $a_3$ | Τ       | $a_5$ |

|---|---|-------|-------|-------|---------|-------|

| - | В | $b_1$ | $b_2$ | 1     | 1       | $b_5$ |

|   | Y | $a_1$ | $b_2$ | $a_3$ | $\perp$ | $a_5$ |

Figure 1.8: The operation of default in SIGNAL

The default operator has an important theoretical consequence: faster clocks can be generated by means of this structure than the clock of any input.

#### • Process composition

SIGNAL equations shown above are considered *elementary processes*. The structure

allows for creating a new process from system of equations. In this new process common signal names denote common signals.

SIGNAL compiler uses a very elegant method called *clock calculus* for checking certain properties of the program and for generating the execution scheme. SIGNAL programs are transformed into boolean equations to express the presence of signals and boolean operations and dependency graphs to describe data dependencies of non-boolean functions. Integer values are assigned to signal states as the following:

$$true \longrightarrow +1$$

$$false \longrightarrow -1$$

$absent \longrightarrow 0$

$present \longrightarrow \pm 1$

Operations on these values are made modulo 3, the field consisting of the values above and the operations will be denoted  $\mathcal{F}_3$ . A signal is represented as x and  $x^2$  represents its clock. With these notations y := a+b can be

coded as the following:

$$y^2 = a^2 = b^2, \quad a \xrightarrow{y} \quad y, \quad b \xrightarrow{y} \quad y$$

The above equations mean that y, a, b all have the same clock and  $a \longrightarrow y$ and  $b \longrightarrow y$  dependencies hold when the common clock of y, a, b signals  $y^2$ is present. The description above is extended to all the SIGNAL operators [LeG91]. For example in the case of default:

In the case of boolean signals:

$$y = u + v(1 - u^2)$$

In the case of non-boolean signals :

$$y^2=u^2+v^2(1-u^2), \quad \begin{array}{ccc} u^2 & & (1-u^2)v^2 \\ u & \longrightarrow & y \end{array}, \quad v \quad \begin{array}{cccc} & & & y \end{array}$$

It means that the clock of y will be the clock of u if present, else the clock of v. y will depend on u if present else on v if present.

Systematically using the method above means will result in a conditional dependency graph and attached clock equations. The following simple equation set

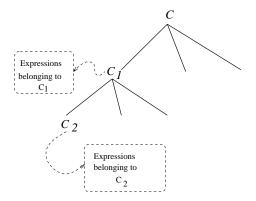

has the dependency graph depicted in fig 1.9.

When SIGNAL compiler translates a SIGNAL program into sequential executable it builds a clock tree [Amag94]. This clock tree is constructed like the following

• We call free boolean signals the inputs, values resulted in the evaluation of boolean expressions and values from boolean memories. Clocks defined by the true value of a free boolean signal (when C) and clocks defined by the false value of that signal (when not C) are called downsamplings of that signal and inserted into the subtree of the boolean signal.

Figure 1.9: Conditional dependency graph of the example program

• If K lies under H then all instants of K form a subset of instants of H

We get this way a set of interconnected trees that we call *forest*. The forest may or may not have one common root, in the latter case the system does not have a single master clock.

Pieces of the conditional graphs are attached to this clock tree thus yielding the *conditional hierarchical graph*. The signals available at a given clock are connected to this clock in the tree and also the expressions which define these signals. The resulting graph is the base of code generation. Figure 1.10 depicts the scheme.

Figure 1.10: A conditional hierarchical graph

The code generation is based on nested if ... then constructs. Clocks are represented as boolean variables and the following structure is generated from the graph in fig. 1.10

```

if C then

if C1 then

... operations belonging to C1 come here in

dependency order ...

if C2 then

... operations belonging to C2 come here

in dependency order ...

endif

endif

```

The SIGNAL compiler is capable of generating C and Fortran sequential code or an intermediate format for the SynDEx parallel code generator [Sor94]. The last extension of the language (SIGNALGTI, [March95]) introduces time intervals and preemptive tasks to the language.

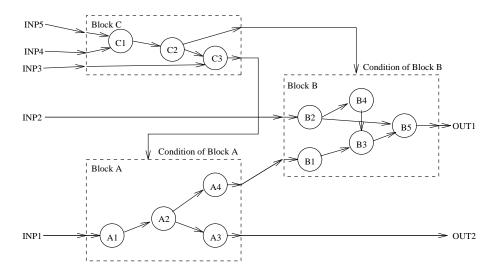

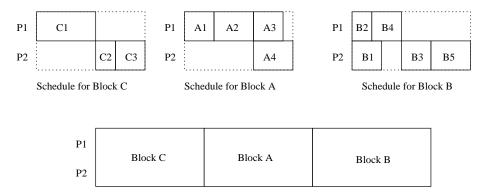

#### 1.3.4 SFG generation from synchronous description

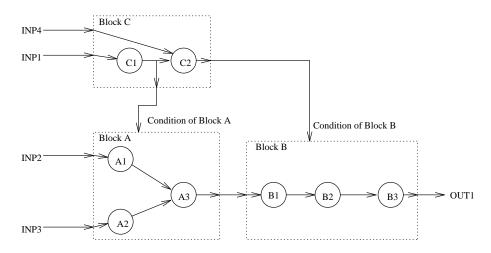

We have presented three synchronous languages and we went into details how sequential program is generated from the concurrent description in the case of SIGNAL language. As we have already mentioned in section 1.2.3, the consistence of BDF graphs in general case can be difficult to prove. On the other hand, synchronous languages readily generate conditional dataflow graphs. We can exploit therefore the sophisticated proofing mechanisms of these languages and suppose much simpler dataflow graph constructs than the general BDF case. These important simplifications are the following:

- SIGNAL compiler groups the operations having the same condition together and resolves their dependency orders. We have therefore blocks of dataflow graph pieces assigned to their conditions as result of compilation.

- Biggest weakness the SIGNAL language is blamed for in [Buck93b] is that it allows only one token on every arc, token queuing is not supported. Correct SIGNAL program thus cannot describe dataflow system where an arc needs unbounded memory that must be allocated dynamically, in run-time. [Buck93b] mentions this fact as a disadvantage (context-free grammar parser that needs probably unlimited stack cannot be implemented in SIGNAL ...) but this restriction greatly simplifies the memory allocation scheme of the multiprocessor code generator attached to SIGNAL compiler.

• The condition scheme we get from SIGNAL compiler is consistent. An SFG compiler processing output of SIGNAL compiler must not deal with the problem whether the graph it transforms into multiprocessor code is consistent or not.

The approach of generating multiprocessor code from SIGNAL's output has already been used in the SynDEx environment [Sor94] and we will exploit the simplifications above when presenting the software models of the Rafael system.

# Chapter 2

# The static scheduling problem

#### 2.1 Problem formalization

First we modelize both the algorithm to be scheduled and the target hardware. We use the following model for the algorithm.

- We suppose a problem which can be described by static data flow. The real restriction that we impose is that we know the precise dependency graph. As it was described in the introduction the creation of acyclic precedence graph from the general dataflow graph is not an evident question in the case of BDFs. We suppose this problem solved.

- The precedence relations among the tasks can be represented as a directed acyclic graph. Nodes in this graph represent operations, branches represent precedence constraints.

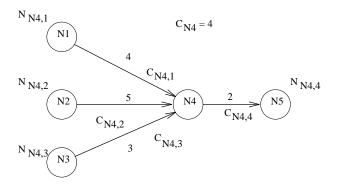

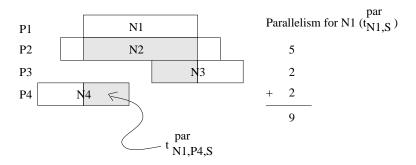

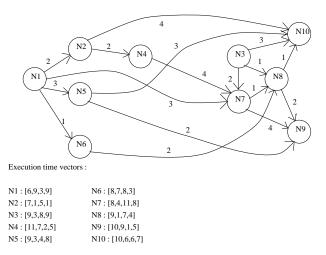

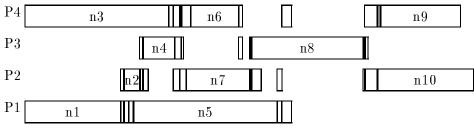

- We decorate this graph, we call the decorated version Decorated Acyclic Precedence Graph (DAPEG). Execution time vectors are attached to each node. Execution time vector contains the time necessary to accomplish a task on a certain processor.

- Branches of the precedence graph are decorated by the amount of data units transferred through them when the operation node at the input of the branch is fired.

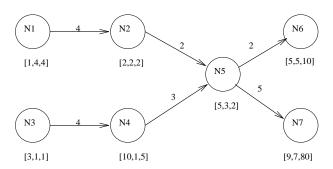

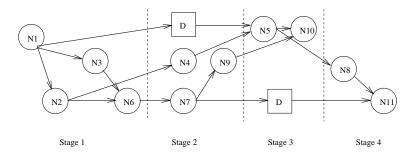

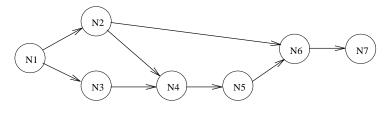

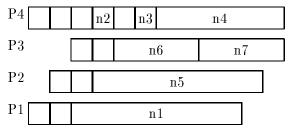

An example DAPEG can be seen in figure 2.1.

Figure 2.1: A decorated acyclic precedence graph

We will use the following notations: we have a G(V, E) acyclic precedence graph where V is the set of nodes, E is the set of edges. The graph contains N nodes (N = card(V)) and we will denote one node as  $n_i \in V$ . We say that  $n_i$  is immediate predecessor of  $n_j$  if there exists a directed edge from  $n_i$  to  $n_j$ . In this case we will say that  $n_i = prev(n_j)$  and  $n_j = succ(n_i)$ . We attach the computation time vector to each node:

$$\overline{t}_{n}^{e} \equiv [t_{n,1}^{e}, t_{n,2}^{e}, \dots t_{n,P}^{e}], 1 \le n \le N$$

where P is the number of the processors in the target hardware and  $t_{n,p}^e$  is the execution time  $t^e$  of node n on processor p.

The modelization of the target hardware is a harder task. The scheduling problem is just enough complex so the hardware model is often simplified in many approaches. First, most frequent simplification is that the target hardware is homogeneous so it contains the same type of processors. This restriction must be relaxed because of the importance of mixed-type realizations. Other accepted simplification area is the communication model. Realistic modelling of the wide variety of communication hardware is not an easy task. In the common DSP hardwares the following main types of communication hardwares exist:

- There is no need for communication hardware in VLSI realizations where the internal operation connections are made via wires and it takes no time to communicate thorugh them.

- Programmed communication without hardware support. Several custombuilt low speed communication hardware of cheaper DSPs fall into this cathegory.

- Programmed but interrupt-supported communication hardware. Almost every cheaper DSPs (Texas TMS320C25, Motorola DSP56000) has some means of communication (serial lines, parallel interfaces) which are supported by interrupt-driven software.

- DMA-supported communication hardware in the more expensive (Texas TMS320C40, Motorola DSP96000) DSPs and in the Transputers (T800, T9000).

- Shared memory in custom DSP realizations and in the Texas TMS320C80 multi-DSP chip.

- Dedicated communication hardware (communication coprocessors) in massively parallel computers.

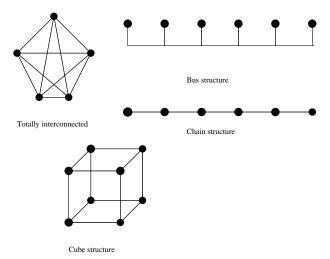

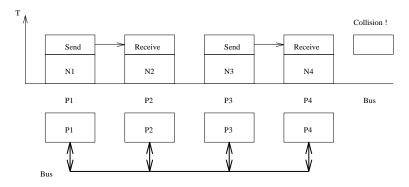

As we advance on the list, each form of communication is more sophisticated and require less processor overhead. Other important question is the *communication topology*. The simplest one is the totally interconnected structure which is suitable only for smaller processor numbers. Fig. 2.2 shows some of the more frequently used topologies.

Figure 2.2: More frequently used communication topologies

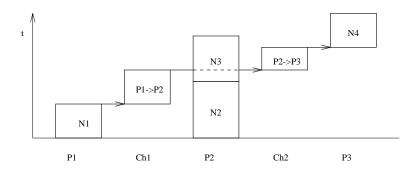

The communication activities can be dynamically or statically scheduled as the operations. Dynamically scheduled communication needs a *communication layer* which works in the background. This layer processes autonomously the communication tasks, sends the messages in the background,

passes the received messages up to the computation layer, forwards messages whose destination is an other processor. This solution is easier to realize than the totally static communication where all the communication activities are scheduled together with the computations. Big drawbacks of the dynamically scheduled communication are that computation durations are more difficult to estimate (because of background tasks' processor load) and the dynamic scheduler, interrupt handler, etc. waste processor time.

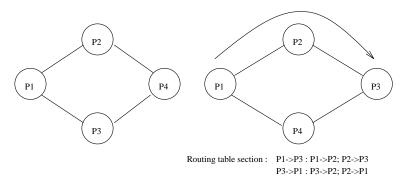

A scheduling algorithm which has to consider the effect of the communication must calculate a correct estimate of the communication time necessary to pass a data block between two processors. In the case of more complex communication scheme this estimation is not an obvious task. If the communication activities use shared communication channels, the interference of the messages passing on the same channel must be considered. If the communication activities are scheduled statically as well (so there is no underlying communication layer) and the communication graph is not entirely connex (messages must travel through intermediary processors to reach their target) the schedules on the intermediary processors must also be considered.

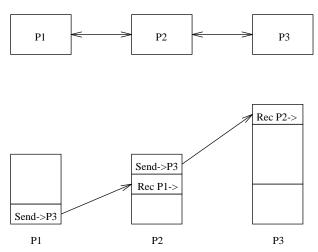

Figure 2.3: The effect of the schedule on the communication

Because of the difficulties of the exact communication modelling, simplifications are frequent. Following approaches are common:

1. Communication costs are neglected. This approach is acceptable only in the case of very coarse-grain DAPEGs or hardware realizations. In

fact, VLSI design algorithms never consider internal communication costs.

- 2. Uniform communication cost is supposed for every communication link. This model is acceptable in the case of totally interconnected topology with the same type of communication links.

- 3. Different communication cost for each communication links. This approach tries to offer an acceptable model for the effects of the message forwarding and bus occupation. Higher communication costs are given to "farther" processors (if the message must be routed through an other processor, for example).

- 4. Full modelling of the communication hardware including correct communication channel scheduling and operation scheduling interference.

Modern scheduler algorithms use only the 3rd and 4th models. The problem with the 3rd model is that it does not consider communication channels as resources and it may seriously underestimate the necessary communication time if there are many requesters for one channel. The 4th point is problematic because - as we will see - the scheduling problem is just enough complicated without communication channel scheduling. This results in the fact that the 4th model is employed only by simpler schedulers which produce much worse quality results than the more complicated ones while more efficient schedulers stick at the 3rd model acknowledging its inexactness. Our schedulers use the 3rd model as well but in section 2.5 we will present a version of our scheduler using the 4th model.

## 2.2 Static scheduling methods

In the following we give a quick overview on the existing scheduler algorithms before presenting the schedulers used in Rafael.

#### 2.2.1 ASAP and ALAP schedules

These most basic scheduling methods are the As Soon As Possible and As Late as Possible algorithms. If we have unlimited resources, these algorithms produce minimal-length schedules but the resource utilization can be suboptimal. The algorithm was presented first in Hu's classical publication

[Hu61]. ASAP scheduler starts operations as soon as all the predecessor nodes terminate the computation that is

$$E(n_i) = max(E(pred(n_i))) + t_i$$

(2.1)

where  $t_i$  is the execution time of node i and  $E(n_i)$  is the earliest time when  $n_i$  can be executed. Nodes with no predecessors has E=0. This simple version is only for homogeneous architectures. The original version supposes unlimited resources and schedules nodes just at their E.

ALAP schedule is based on very similar principles. Nodes are scheduled as late as possible without increasing the length of the schedule.

$$L(n_i) = min(L(succ(n_i))) - t_i$$

(2.2)

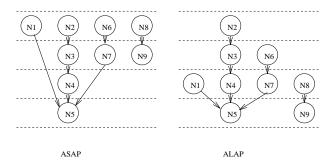

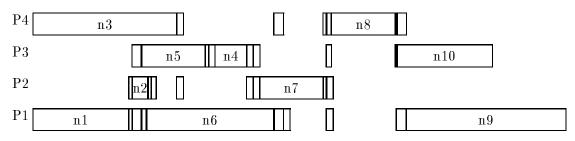

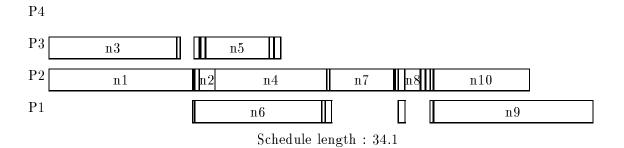

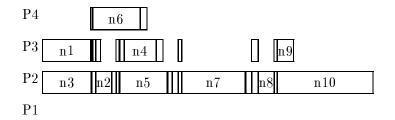

$L(n_i)$  is the latest time when  $n_i$  can be executed in the case of minimal length schedule. L values of nodes with no successors are initialized to the maximal E value over the entire graph. Figure 2.4 depicts the ASAP and ALAP schedules of an example graph.

Figure 2.4: ASAP and ALAP schedules

#### 2.2.2 Integer Linear Programming (ILP)

[Lee89a] presents an algorithm for VLSI data path synthesis which produces optimal solution. This algorithm leads back the scheduling problem to a linear optimization task. The basic version of this algorithm supposes the common restrictions in data path synthesis:

- Each operation has one cycle propagation delay

- Communication is costless

The algorithm is capable of finding minimal-length schedules but unlike ASAP and ALAP this method allocates minimal number of computation resources. The optimization task is formulated as a set of linear equations. The formulation uses the following variables:

- 1.  $M_{t_i}$  integer variables which denote the number of computation units of type  $t_i$  needed. ( $t_i$  can be multiplier type, comparator type, etc.)

- 2.  $x_{i,j}$  are 0-1 integer variables.  $x_{i,j} = 1$ , if node i is scheduled at time step j, 0 otherwise.

We will denote the cost of a computation unit of type  $t_i$  ( $FU_{t_i}$ ) as  $c_{t_i}$ , there are m types of computation units and let S be the length of the ASAP and ALAP schedules (number of control steps required).

First we make the ASAP and ALAP schedules thus determining S, ASAP and ALAP times. Now the minimization problem is the following: we want to minimize

$$\sum_{i=1}^{m} c_{t_i} \cdot M_{t_i} \tag{2.3}$$

with the following restrictions:

$$\sum_{i=1, n_i \in FU_{t_k}}^{N} x_{i,j} - M_{t_k} \le 0, \qquad \text{for} \qquad 1 \le j \le S, 1 \le k \le m \qquad (2.4)$$

Eq. 2.4 expresses that in each control step at most  $M_{t_k}$  computation unit of type  $t_k$  can be used.

$$\sum_{j=E_{n_i}}^{L_{n_i}} x_{i,j} = 1, \qquad \text{for} \qquad 1 \le i \le N$$

(2.5)

which means that only one  $x_{i,j}$  variable can be 1 in the ASAP-ALAP range for each operation.

$$\sum_{j=E_{n_{i}}}^{L_{n_{i}}} j \cdot x_{i,j} - \sum_{j=E_{n_{i}}}^{L_{n_{i}}} j \cdot x_{k,j} \le -1 \qquad \text{for all} \qquad n_{i} = pred(n_{k}) \qquad (2.6)$$

Eq. 2.6 forces the precedence constraints so that each predecessor operation be scheduled before all its successors. The equation set yielded is then

solved by a linear programming package. [Lee89a] extends the method to multicycle operations, pipelined data paths and mutually exclusive operations.

Big disadvantage of the ILP method is that its computational requirement quickly becomes intractable [Gajs92]. For example if we increase the control step by 1, it means N new  $x_{i,j}$  variables. There were efforts to split the problem into smaller parts and use ILP for the subproblems only [Hwang93] but ILP is still unpractical for larger problems.

## 2.2.3 Branch & Bound algorithms

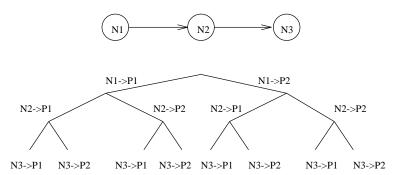

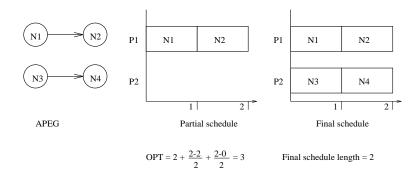

Other well-known approach used mainly in the artificial intelligence fields is the decision tree search. If we evaluate all the possible solutions, we must find the best. See fig. 2.5 for a decision tree of a simple scheduling problem.

Figure 2.5: Decision tree of a simple APEG on a two-processor system

As we could easily see, the number of leaves on the tree - thus the combinations to be evaluated - is  $P^N$ . An algorithm which traverses the whole tree has exponentional complexity and it produces inacceptable execution time even in the case of very small problems. Heuristic methods are used to "purge" the decision tree. "Purging" the tree means that some combinations are eliminated based on heuristic rules. The resulting algorithm is called  $\operatorname{Branch} \operatorname{\mathscr{E}} \operatorname{Bound}$  class which includes broad variety of solutions. First publication of B&B for the scheduling problem appears to be [Green87].

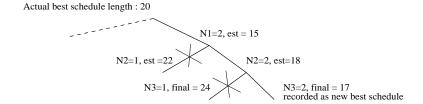

In [Green87] two heuristic functions are presented to predict the length of the final schedule from the partial schedule. The algorithm maintains a "length of the best schedule found so far" variable. At the beginning this variable is not valid. First we start at the root of the decision tree and we make a tentative decision, for example we suppose N1 to be scheduled on P1.

We evaluate the heuristic estimation function and compare the result with the best schedule found so far (if this variable is not valid yet, we consider the result "less"). If the comparation yields "greater" result, we ignore that branch of the decision tree and make a new tentative decision. If the result of comparation is "less", we advance on that branch of the decision tree and we schedule a new node. If we got to a final schedule and its length is less than the best schedule, we record the best schedule and its length and step back to the previous level of the decision tree. Fig. 2.6 illustrates the method.

Figure 2.6: Purging the decision tree in the Branch & Bound algorithm

The heuristic function has critical role in the utility of the B&B algorithm. If it underestimates too much the schedule length, too few branches will be purged and the execution time will be inacceptable. If it overestimates, however, branches leading to the best solutions may be cut.

[Green87] introduces three heuristic functions called OPT,H1 and H2. OPT produces smaller estimates than H1 and H2. The OPT function generates the largest number of nodes. Let  $f_i$  be the time when processor i becomes free (finish time of the last operation scheduled on it) and

$$W = \sum min(\vec{t_n})$$

for all the operations not scheduled so far (2.7)

With these notations:

$$OPT = max(f_i) + max(0, \sum_{i=1}^{P} \frac{W - f_i}{P})$$

(2.8)

[Green 87] claims that OPT never overestimates the final completion time. It is not true, see fig. 2.7 for an example. Other simplified function which generates less nodes is called H2. H2 assumes that tasks not in the partial schedule will have the same average execution time as the tasks in the partial schedule.

Figure 2.7: A case when OPT overestimates the final schedule length

$$H2 = N \cdot \frac{max(f_i)}{\text{tasks in the partial schedule}}$$

(2.9)

The referenced article uses H2 only after 20% of the tasks has been assigned because the value of H2 varies widely at the beginning. Communication costs are not taken into account in this approach.

There were many efforts concerning the usage of the B&B style algorithms for solving the static scheduling task. [Chow91] presents the well-known  $A^*$  algorithm in static scheduling application and [Konst90] describes a B&B-style algorithm which is able to consider communication cost as well. Advantage of the B&B methods is that it is capable of supporting heterogeneous architectures without difficulty. The biggest disadvantage is that in spite of the decision tree cuts, B&B still has exponential complexity in average so its evaluation can be very costly. We will see that algorithms in polynomial complexity can produce as good results as B&B methods in exponential time.

#### 2.2.4 General List Schedulers

By far the simplest and most popular method is the list scheduler algorithm. Huge number of applications has been published based on list schedulers. The basic idea is very simple. We have a ready node list which contains all the nodes that can be executed at the moment. First it is initialized to nodes with no predecessors. Heuristic functions are used to pick a candidate node among the nodes in the ready list and choose a processor for it. This node is scheduled on the processor chosen, removed from the ready list and the successor nodes whose all predecessors have been assigned are inserted

into the ready list. The algorithm terminates when the ready list becomes empty.

The interesting part here is the heuristic which selects the candidate node and/or the appropriate processor for it. The simplest approach is based on ASAP level: nodes with smaller ASAP levels are scheduled first [Tseng86]. More advantageous approach is to delay the nodes as late as it does not block the execution of other nodes, this is the ALAP-based scheduling, nodes with the lowest ALAP levels are scheduled first [Kung85]. Combination of the two approaches is the mobility or freedom-based scheduling. The mobility is the difference between the ALAP and ASAP time, operations on the critical path has 0 mobility. An operation belongs to the critical path if it cannot be delayed without increasing the length of the schedule. In the mobility-based schedulers [Pang87, Goos87, Mirch88] nodes with lower mobility will be scheduled first.

We will examine here a little bit more in detail an ALAP-based scheduler which is used in the SynDEx system [Sor94] as we will use both the system and the scheduler as reference.

SynDEx scheduler is an ALAP-based scheduler whose cost function is :

$$J_{n_i,p} = t_p^{start} - t_{alap} (2.10)$$

where  $t_p^{start}$  is the earliest time when the execution of node i can be started on processor p taking into account the finish time of the operations on that processor and the time necessary to pass each variable needed by the operation from other processors.

The node-processor selection part is rather complicated.

- 1. First the best processor is found for every ready node. The best processor is the one on which the node achieves the minimal start time.

- 2. We look for the node with the best (earliest) start time and we will denote it earliestcandidate. We define the limit date variable as the following: limit date = start time of earliestcandidate + duration of earliestcandidate.

- 3. We evaluate the cost function for each ready node whose start time is smaller than the limit date. We pick the node with the highest cost (most urgent to execute) and we schedule it on its best processor.

We will evaluate this method in section 2.3.

In their very influential and frequently referenced article Paulin and Knight [Paul89] introduced a sophisticated heuristic function using "forces" to describe how necessary it would be to assign an operation to a functional unit. The force calculation considers the effect of the preceding assignments and the effect of the assignment on successor nodes as well. Advantage of the method is that it parallely considers the effect of scheduling of all the nodes and also their successors.

One of the most advanced list scheduler (practically the state of the art) was introduced in [Sih93a], the DLS scheduler. DLS uses a very complicated heuristic function in which

- 1. the communication time

- 2. heterogeneous target system

- 3. descendant consideration

- 4. resource scarcity (how important it is that a certain node obtain a certain processor)

are taken into account. We will use DLS as a reference algorithm for performance evaluations of our algorithms.

### 2.2.5 Graph partitioning algorithms

The rather fuzzy class name in the section title denotes algorithms which cut the graph into pieces first using heuristic methods then schedule these partitions on processors. These algorithms are the most complicated heuristic schedulers and on homogeneous architectures these methods produce the best results.

The linear clustering technique groups the most expensive paths into linear clusters [Kim88]. Linear cluster is a degenerate tree in which every node has exactly one predecessor and successor. In each iteration the most expensive path (both in communication and in computation) is grouped into a linear cluster and nodes belonging to this path are removed from the graph. The resulting clusters are then mapped to the processor architecture using graph-theoretic techniques.

The internalization technique [Sark89] clusters nodes together in order to minimize the schedule length on an unbounded number of processors. First each node is put into different clusters then the algorithm tries to unify clusters. Two clusters can be merged if there are communication between

them, the algorith tries to "internalize" the communication between clusters. A clustering step is accepted if it does not increase the length of the schedule else the clusters remain unmerged and the next arc is considered. The schedule length estimation algorithm is similar to critical path methods. First the earliest and latest start time of the nodes are calculated similarly to the ASAP-ALAP method taking into account the communication times. The main difference is that now we enforce that nodes in the same cluster be scheduled on the same processor. We suppose unbounded number of processors in this pass. When the clustering phase finishes, a modified list scheduler is used to assign clusters to processors. This list scheduler tries to assign each unassigned cluster on each processor and maps the cluster to the processor which yields the minimum execution time.

Figure 2.8: NBranch and IBranch instances and arc cuts

In [Sih93b] a complex method is presented which produces even better clusters than the previous algorithms. We describe the method only briefly here, interested reader should consult the referenced article.

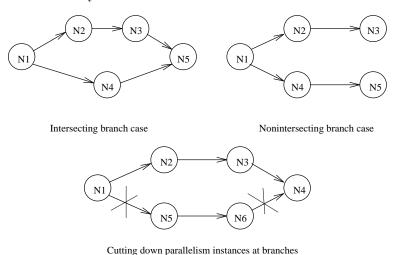

• First the reachability set is determined for each node. If node j is in the reachability set of node i it means that precedence constraint (direct or indirect) exists between the two nodes, node i must be executed before node j. Then branches of the graph are categorized to intersecting and nonintersecting branches. A branch is intersecting if  $RS(B) \cap RS(C)$  is nonempty (where RS(B), RS(C) are the reachability sets of the branch nodes), nonintersecting else.

- The branch instances are inspected whether it is worth cutting down one branch. We verify whether we gain by parallelism or loose by communication cost by scheduling the parallelism instance on an other processor. If we gain, the branch is sliced down (are sliced down in the Ibranch case) and is registered as a new cluster.

- The clusters are grouped hierarchically. At each step the clusters which communicate the most are selected and merged.

- Declustering. We take the two top clusters in the cluster hierarchy and shift some of them to candidate processors selected according to communication costs and we verify, if we yield better schedule than the actual one and save this schedule if it is better. Then we move to the next cluster pair in the hierarchy tree.

As we could see, all the schedulers in this section depend heavily on the fact that speedup can be yielded only by maximizing parallelism exploitation and minimizing communication load. Neither of them is able deal with heterogeneous architectures.

# 2.3 The Rafael heterogeneous list scheduler (RHLS)

The first Rafael scheduler was developed for really rapid prototyping, for this reason we chose a list scheduler. Experiences got with RHLS shown us what we can expect from a list scheduler. RHLS is an ALAP-based scheduler which was made suitable for heterogeneous environment.

In the first step we create ASAP and ALAP schedules in order to get the ALAP levels. (See section 2.2.1). We assume that we can always schedule the nodes on the fastest processor possible so minimum execution time is supposed when building the ASAP-ALAP schedules. Then we launch the list scheduler as it was described in section 2.2.4.

$$t_n^{e,asap}=min(\overline{t}_n^e)$$

Then we define urgency of the operation n like the following:

$$u_{n_i} = L_{n_i} - t_v \tag{2.11}$$

where  $t_v$  is the *virtual time* and it will be detailed later.

The base of the scheduling heuristic is to assign the nodes on the critical path to the fastest processor available. The more urgent it is to execute a

node (as its delaying would set back the execution of the whole graph) the faster processor it deserves. The most urgent nodes are those which have the lowest ALAP time.

We pick hence the node to be scheduled, we need the best processor to execute it. The best processor selection is very simple: we try the node on each processor considering the communication costs and we pick the one on which the node achieves the earliest completion time. Before trying a node on a processor, necessary communication activities are scheduled tentatively so that we know how much time must be calculated for fetching the input variables produced on other processors.

The heuristic algorithm works like the following:

```

Create the ready node list from nodes that has no

predecessors

while the ready list is not empty do

for all nodes do

if u(i) < minimum so far

Candidate = node i;

end for

Try the candidate on each processor

considering communication cost;

Choose the processor on which the task achieves

the earliest ending time;

Schedule candidate node and the necessary

communication activities on candidate

processor;

Update u(i)s and tv;

Add nodes that become ready to the ready list;

end while

```

As the real  $t_{n_i}$  node starting times will generally not be equal to the ideal ASAP or ALAP starting times the scheduler maintains real processor times and  $t_v$  virtual time. The virtual time is used to track the time in the ALAP schedule graph while the real time is the scheduling time on the processors. The  $t_v$  variable shows where we are in the ALAP schedule graph, it is set to the lowest ALAP time among the ready nodes. The last step is the updating of urgency and virtual time variables.

We evaluated RHLS with two reference algorithms: SynDEx and DLS (see section 2.2.4). The prototypes of the three algorithms were realized

| alg/RHLS results(%) | worst  | best | average |

|---------------------|--------|------|---------|

| DLS                 | -21.95 | 6.96 | -5.7    |

| SYN                 | -10.10 | 7.24 | -1.92   |

Tableau 2.1: Performance comparation of RHLS with the reference algorithms

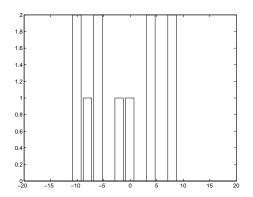

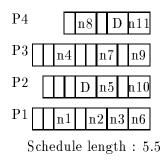

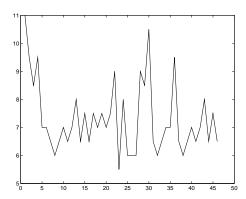

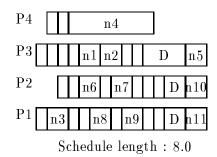

in Lisp and a 21-member set of DAPEGs was generated randomly. The execution time of the nodes was in the 1-10 interval, the number of the nodes was between 25 and 50, the set was homogeneous as SynDEx could not support heterogeneous architectures. Communication times were not generated randomly, we used a chain-like model where farther processors had bigger communication cost. The graphs were scheduled by each algorithm and the following ratio:

$$\frac{t_{alg}^{sched}}{t_{BHLS}^{sched}} 100\% - 100\%$$

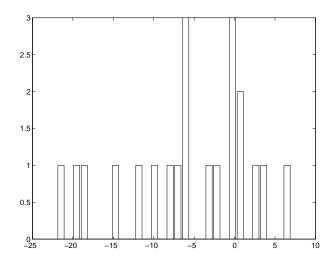

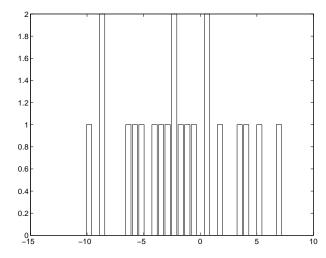

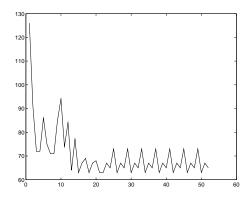

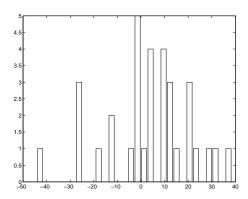

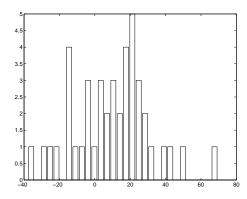

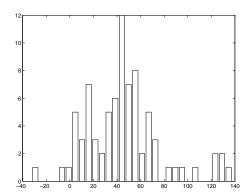

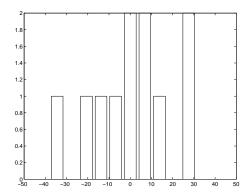

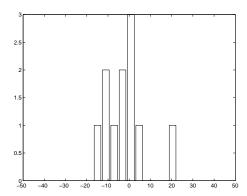

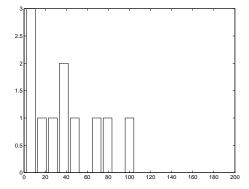

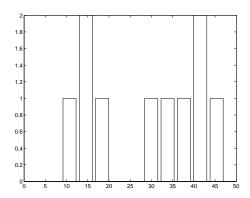

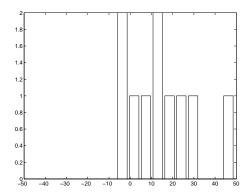

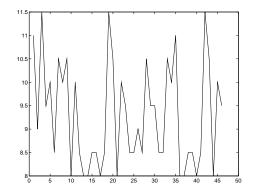

was calculated wher  $t_{alg}^{sched}$  is the length of the schedule produced by the reference algorithm and  $t_{RHLS}^{sched}$  is the length of the schedule produced by RHLS. The worst, best and average performance ratios can be seen in table 2.1 and the histograms of the performance ratio distribution is depicted in figures 2.9 and 2.10.

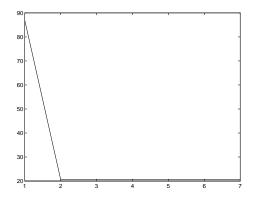

As we can see the more complicated the heuristic rule is more cases there are when it fits well the problem. The complexity of the heuristic rule , however, is not proportional with the performance gain. The very complex DLS heuristic rule gains only about 6% over RHLS and less than 4% over SynDEx in average and there are numerous cases when the simpler algorithms produce better schedules. This disappointing experience diverted us from the list schedulers and urged us to develop new scheduler methods.

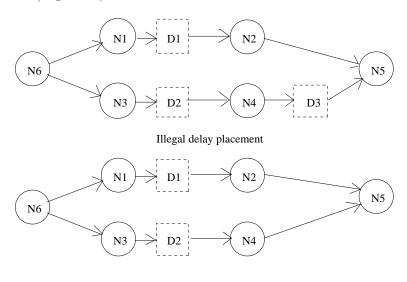

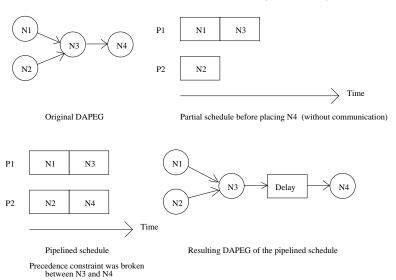

# 2.4 Nonpipelined Springplay algorithm

The heterogeneous environment adds a new dimension of liberty to the scheduling problem so the complexity of the problem increases significantly. The - even partial - search of the decision tree or a formal ILP solution are proved to produce inacceptable execution times. Inspired by the success

Figure 2.9: Distribution of DLS/RHLS results, 21 samples

Figure 2.10: Distribution of SYN/RHLS results, 21 samples

of Hopfield class of neural networks in solving optimization tasks [Hopf85, Pars87, Mitt93, Rabe93] and by a very graphic representation of affectations in the Force-Directed Scheduling algorithm [Paul89] we devised a new class of heuristic scheduler that we call global heuristic optimizer. In this method no decision is made but the heuristic rule is used to affect the state of the resolver system. This system is constructed in such a way that it converges toward the optimal solution. Springplay algorithm is the first application of this global optimizer idea [Pall95].

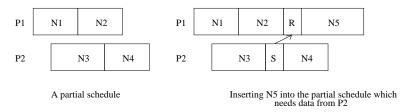

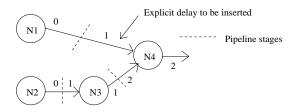

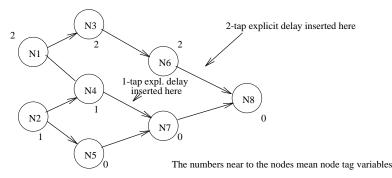

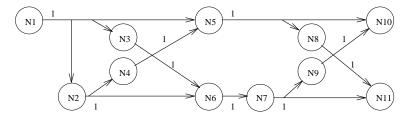

## 2.4.1 Principles of the Springplay algorithm